## **Agilent N8241A Arbitrary Waveform Generator Synthetic Instrument Module** 1.25 GS/s or 625 MS/s

**Technical Overview**

The Agilent Technologies N8241A arbitrary waveform generator (AWG) is capable of creating high-resolution waveforms for radar, satellite, and frequency agile communication systems.

- 15 bits of vertical resolution per channel and either 1.25 Gigasamples per second (GS/s) or 625 Megasample per second (MS/s) provides exceptionally realistic wideband waveforms

- Dual output channels drive both single-ended and balanced designs without the need for baluns or hybrids

- · Extended waveform memory and advanced sequencing engine offers long scenario simulations

- · Multiple module synchronization provides multi-emitter simulations

- Multiple programmatic interfaces enable easy integration into existing test environments

- Fully compliant to LXI Class A standards

## Generate wide bandwidth AND wide dynamic range signals. simultaneously

Each channel of the N8241A operates at either 1.25 GS/s sample rate (Option 125) or 25 MS/s sample rate (Option 062) and features 15 bits of vertical resolution giving designers the most realistic, wideband waveforms available from a commercial AWG. This LXI synthetic instrument module offers dual differential output channels to drive both single-ended and balanced designs. The AWG also supports advanced sequencing and triggering modes to create event- based signal simulations. Multiple N8241A modules can be synchronized for the generation of phasecoherent, multi-emitter scenarios. Waveform development tasks are simplified using the AWG's numerous programmatic interfaces including complete instrument control from the MATLAB® command line. When the N8241A is combined with a wideband I/Q upconverter, modulation bandwidths of 1 GHz can be realized at microwave frequencies for authentic signal simulations for IF and RF subsystem test.<sup>1</sup>

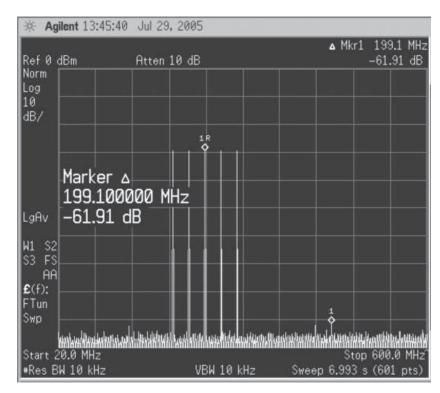

Figure 1. Generate wide band waveforms with unprecedented signal fidelity.

#### **Unprecedented performance**

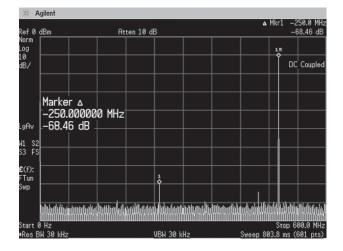

The N8241A gives designers access to the most advanced Digital-to-Analog (DAC) technology available in a commercial AWG. Each module incorporates two high-speed DACs to create 500 MHz of signal bandwidth and  $\leq$  –65 dBc spurious free dynamic range (SFDR) across each channel. Users have the choice of driving their designs differentially from the DAC outputs or single-ended through multiple signal-conditioning paths.

Although some AWGs require users to make a trade-off between the number of output channels and differential outputs, the N8241A provides both — allowing you to drive your designs and eliminating the need for baluns or hybrids in the test path. In addition, each channel can output waveforms as an IF or as a baseband signal for I/O upconversion.

<sup>1</sup> Agilent E8267D PSG signal generator with Option 016, wideband I/O inputs or Agilent N8211A performance vector upconvertor with Option 016; either option could be used.

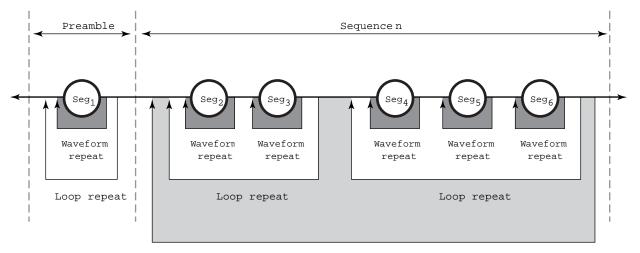

Sequence repeat

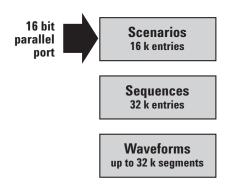

Figure 2. Create sophisticated signal scenarios by looping and nesting waveforms.

#### **Create long scenario simulations**

Multiply the effective size of on-board memory through the use of the N8241A's advanced sequencing engine. Uniquely define how waveform segments are played through looping and nesting of stored waveforms. This capability also gives users the ability to create new signals from existing waveforms by playing only subsegments of waveform memory.

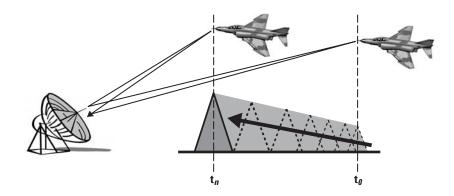

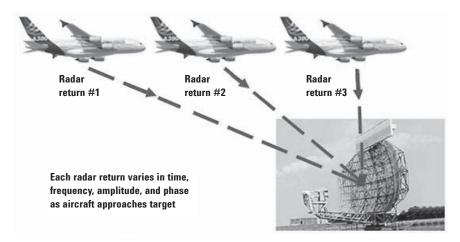

Figure 3. Closing targets can be simulated by ranging parameters on each pulse.

### **System scalability**

Create phase-coherent, multi-emitter simulations using the N8241A's precision SYNC clock. A single N8241A can drive a total of eight AWG modules to synchronize their outputs on a sample-by-sample basis. Any number of modules can be synchronized with simple driver hardware. The AWG also includes multiple front-panel trigger and markers for complete system synchronization.

#### Ease-of-use

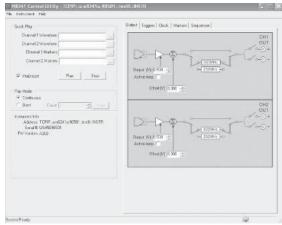

The N8241A's graphical user interface guides developers through module setup and waveform file transfers. Users can quickly configure the instrument's signal conditioning paths, marker and trigger lines, sample and reference clock sources and simple sequencing functions. More sophisticated sequencing functions are available through the instrument's numerous programmatic interfaces. The N8241A supports interfaces for MATLAB, LabView, IVI-C, and VEE framework.

**Figure 4.** The N8241A's compact modular size is perfect for integrating into ATE system racks.

**Figure 5.** Directly import and play waveforms from the Quick Play menu.

Figure 6. Play waveforms files directly from the MATLAB command line.

## **New! Enhanced Capabilities for the N8241**

### **Dynamic Sequencing (Option 300)**

The dynamic sequencing software enables radar and military communications engineers to build custom signal scenarios on the fly. Engineers can dynamically access up to 16 k of previously stored sequences through a 16-bit interface and replay these complex waveforms to respond to changing threat environments, or to create signals where the next waveform to be played is not known in advance.

# Direct Digital Synthesis (Option 330)

The direct digital synthesis (DDS) software enables radar and emerging communications engineers to create basic waveforms in the AWG's memory and then modify their behavior with profiles for amplitude modulation, phase modulation, and frequency modulation. This enables engineers to simulate testing without the time and expense of field trials, such as in-flight and in-orbit testing. This option can also be used to simulate fading profiles in receiver testing for satellite and 4 G signals, such as multiple input, and multiple output formats (MIMO).

**Figure 7.** Create signals where the next waveform to be played is not known in advance.

Figure 8. Define signals by carrier frequency and modulation – instant by instant.

## **Key Characteristics**

| Channels                                  | Two independent channels available as baseband or IF outputs • CH1: Single-ended and differential • CH2: Single-ended and differential                                                                                                                                                                |                                                                                                                                                                                                                                                                                                      |  |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Modulation bandwidth                      | 1.25 GS/s sample rate (Option 125) 500 MHz per channel (1 GHz I/Q bandwidth)                                                                                                                                                                                                                          | 625 MS/s sample rate (Option 062)<br>250 MHz per channel (500 MHz I/Q bandwidth)                                                                                                                                                                                                                     |  |

| Resolution                                | 15 bits (1/32,768 levels)                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                      |  |

| Output spectral purity –<br>(CH1 and CH2) | <ul> <li>1.25 GS/s sample rate (Option 125)</li> <li>Harmonic distortion:</li> <li>≤ -65 dBc for each channel DC to 500 MHz</li> <li>Non-Harmonic spurious:</li> <li>≤ -75 dBc for each channel 1 kHz to 500 MHz</li> <li>Noise floor:</li> <li>≤ -150 dBc/Hz across the channel bandwidth</li> </ul> | <ul> <li>625 MS/s sample rate (Option 062)</li> <li>Harmonic distortion:</li> <li>≤ -65 dBc for each channel DC to 250 MHz</li> <li>Non-Harmonic spurious:</li> <li>≤ -75 dBc for each channel 1 kHz to 250 MHz</li> <li>Noise floor:</li> <li>≤ -150 dBc/Hz across the channel bandwidth</li> </ul> |  |

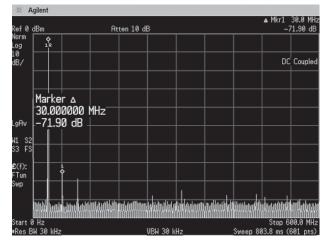

Figure 9. Excellent harmonic and spurious performance are available across the full bandwidth of each channel.

Figure 10. Spurious performance outstanding at low signal frequencies.

| Sample clock<br>Internal                                                                                                                                                                                    | Fixed 1.25 GS/s (Option 125) Fixed 625 MS/s (Option 062)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Internal clock output                                                                                                                                                                                       | +3 dBm nominal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| External clock input                                                                                                                                                                                        | Tunable 100 MS/s to 1.25 GS/s (Option 125) Tunable 100 MS/s to 625 MS/s (Option 062)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| External clock input drive level                                                                                                                                                                            | +5 to –15 dBm typical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Phase noise characteristics                                                                                                                                                                                 | 1 kHz: -95 dBc/Hz<br>10 kHz: -115 dBc/Hz<br>100 kHz: -138 dBc/Hz<br>1 MHz: -150 dBc/Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Noise floor                                                                                                                                                                                                 | -150 dBc/Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Accuracy                                                                                                                                                                                                    | Same as 10 MHz timebase input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Frequency reference<br>Input drive level                                                                                                                                                                    | +2 to +12 dBm into 50 ohms (+2 dBm nominal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Waveform length                                                                                                                                                                                             | 8 MS per channel (16 MS with Option 016)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Minimum waveform length                                                                                                                                                                                     | 128 samples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Waveform granularity                                                                                                                                                                                        | 8 samples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Segments                                                                                                                                                                                                    | 1 to 32 k unique segments can be defined consisting of waveform start and stop address, repetition and marker enable flags.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Segment loops                                                                                                                                                                                               | <ul> <li>A total of 1 million (2<sup>20</sup>) loops can be defined for each segment. Loops can be configured to advance in one of four modes:</li> <li>Single: The segment loop plays once and waits at the end of the loop for a trigger.</li> <li>Continuous: Segment loop is repeated continuously until a trigger is received.</li> <li>Auto: Automatically advances to the next segment after completing the specified number of loop repetitions.</li> <li>Repeat: The waveform loop repeats until the number of waveform loop repetitions is met.</li> </ul> |  |

| Sequences                                                                                                                                                                                                   | Up to 32 k total unique waveform sequences can be defined. A sequence is a contiguous series of waveform segments.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Advanced sequencing                                                                                                                                                                                         | Enables users to build and playback scenarios, which are comprised of one or more sequences.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| enarios  1 to 16 k pointers can be assigned to play pre-defined sequences. Sequence play begins with sequence entry and continues uninterrupted until the last entry is played. The table repeats ustopped. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Sequence jump modes | Sequence jumps determine how a sequence responds to a jump trigger. There are no discontinuities in a sequence jump other than those imposed by the waveform data. Three modes are available to |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | control sequence jumps:                                                                                                                                                                         |

|                     | <ul> <li>Jump immediate: Jumps immediately to the next specified sequence address with a fixed latency.</li> </ul>                                                                              |

|                     | <ul> <li>End of waveform: The current segment (including waveform repeats) is completed before jumping</li> </ul>                                                                               |

|                     | to a new sequence.                                                                                                                                                                              |

|                     | • End of sequence: The current sequence is completed before jumping to a new sequence. Jump                                                                                                     |

|                     | latency is the longer of either the jump immediate latency or the length of the remaining sequence.                                                                                             |

### **Dynamic Sequencing (Option 300)**

| Input                                 | 20-pin mini-D connector                                                                                                                                                         |  |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Input levels                          | All pins configured as 2.5 volt LVCMOS inputs. A logic low must fall within the $-0.2$ to $+0.5$ volt window. A logic high must be within the window of $+2.0$ to $+2.8$ volts. |  |

| Number of address bits                | 13 bits per channel                                                                                                                                                             |  |

| Total number of addressable scenarios | 16 k                                                                                                                                                                            |  |

| Data rate for dynamic data            | 100 ns                                                                                                                                                                          |  |

| Data latency                          | Same as front panel trigger inputs. Software pointers may also be used to point to pre-defined scenarios, though latencies are not deterministic.                               |  |

## **Direct Digital Synthesis (Option 330)**

| Output frequency resolution | 1 Hz                                                      |

|-----------------------------|-----------------------------------------------------------|

| Frequency modulation        | Deviation from 0 to 125 MHz (250 MHz peak-peak)           |

| Phase modulation            | Deviation from -180 to +180 degrees in 0.022 degree steps |

| Amplitude modulation        | Modulation depth from 0 to 100% with 15 bit resolution    |

| Single channel bandwidth    | 400 MHz (800 MHz I/Q)                                     |

### **External triggers**

| Number of inputs                                                                                          | 8 each (4 SMB female front-panel connectors plus four software triggers over the LXI interface from host processor)               |                                                          |

|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Trigger polarity                                                                                          | Negative/positive                                                                                                                 |                                                          |

| Trigger impedance                                                                                         | 2 k ohms                                                                                                                          |                                                          |

| Maximum input level                                                                                       | ±4.5 volts                                                                                                                        |                                                          |

| Input sensitivity                                                                                         | 250 mV                                                                                                                            |                                                          |

| Trigger threshold                                                                                         | -4.3 volts to +4.3 volts                                                                                                          |                                                          |

| Trigger timing resolution                                                                                 | Clock/8 (6.4 ns at 1.25 GS/s rate)<br>(Option 125)                                                                                | Clock/8 (12.8 ns at 625 MS/s rate)<br>(Option 062)       |

| Trigger latency                                                                                           | 34 x clock/8 (217.6 ns at 1.25 GS/s rate)<br>(Option 125)                                                                         | 34 x clock/8 (435.2 ns at 625 MS/s rate)<br>(Option 062) |

| Trigger uncertainty                                                                                       | < 50 ps                                                                                                                           |                                                          |

| Minimum trigger width                                                                                     | 12.8 ns at 1.25 GS/s clock rate<br>(Option 125)                                                                                   | 25.6 ns at 625 MS/s clock rate<br>(Option 062)           |

| Trigger delay                                                                                             | Programmable from 1 to 256 sync clock cycles with 1 sync clock cycle resolution <sup>1</sup>                                      |                                                          |

| LXI triggering modes                                                                                      |                                                                                                                                   |                                                          |

| Driver command based                                                                                      | A driver interface on the controlling computer is used to directly transmit a command to the module.                              |                                                          |

| Direct LAN messaging                                                                                      | A data packet containing triggering information (including a time stamp) is sent directly from one module to another via the LAN. |                                                          |

| Time based events                                                                                         | An IEEE 1588 based time trigger is set and executed internally in a module.                                                       |                                                          |

| LXI trigger bus-based                                                                                     | A module function is triggered via a voltage on the LXI trigger bus.                                                              |                                                          |

| The LXI triggering conforms to the specifications of the LXI standard, revision 1.0, www.lxistandards.org |                                                                                                                                   |                                                          |

<sup>1</sup> A sync clock cycle is clock/8

#### **External markers**

| Markers                          | Can be defined for eac                                                                                               | h waveform segment.                   |                                                |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------|

| Number of outputs                | 4 each SMB female                                                                                                    |                                       |                                                |

| Marker polarity                  | Negative, positive                                                                                                   |                                       |                                                |

| Output impedance                 | 50 ohms                                                                                                              |                                       |                                                |

| Marker low level                 | 100 mV nominal into h                                                                                                | igh impedance load                    |                                                |

| Marker high level                | 3.2 volts nominal into I                                                                                             | nigh impedance load                   |                                                |

| Marker timing resolution         | Clock/8 (6.4 ns at 1.25                                                                                              | GS/s rate) (Option 125)               | Clock/8 (42.8 ns at 625 MS/s rate) (Option 062 |

| Marker latency                   | Marker precedes analo                                                                                                | og output and is adjustable in        | 2 sample clock period steps.                   |

| Marker latency repeatability     | <100 ps                                                                                                              |                                       |                                                |

| Marker width                     | Programmable from 1                                                                                                  | to 256 sync clock cycles <sup>1</sup> |                                                |

| Marker delay                     | Programmable from 8 to                                                                                               | to 502 sample clock cycles, w         | ith 2 sample clock cycle resolution            |

| LXI markers                      | Two LXI markers are a                                                                                                | vailable                              |                                                |

| Module synchronization           | Supports system scalir                                                                                               | ng for any number of N8241A           | modules. A single module can support a fan-out |

| of                               | 8 N8241A modules for precise triggering and repeatability. Driver boards may be used to scale any number of modules. |                                       |                                                |

| Sync clock output level          | 800 mV p-p (50 ohms, AC coupled)                                                                                     |                                       |                                                |

| Sync clock input sensitivity     | 100 mV p-p minimum i                                                                                                 | nto 50 ohms AC coupled                |                                                |

| Analog output                    |                                                                                                                      |                                       |                                                |

| Output connector                 | SMA female                                                                                                           |                                       |                                                |

| Output impedance                 | 50 ohms                                                                                                              |                                       |                                                |

| Analog output levels             | The following output le                                                                                              | evels are specified into 50 ohn       | ns                                             |

|                                  |                                                                                                                      | Single-ended                          | Differential                                   |

|                                  | Passive mode                                                                                                         | 0.5 Vp-p                              | N/A                                            |

|                                  | Active mode                                                                                                          | 1 Vp-p with ±0.2 V offset             | N/A                                            |

|                                  | Direct DAC mode                                                                                                      | N/A                                   | 1 Vp-p (0 volt offset)                         |

| Uncorrected passband flatness    | ±1 dB DC - 200 MHz; ±                                                                                                | -2.5 dB DC - 500 MHz (with 1.         | 25 GHz clock)                                  |

| Uncorrected passband group delay | ±500 ps DC - 200 MHz; ±1 ns DC - 500 MHz (with 1.25 GHz clock)                                                       |                                       |                                                |

| Reconstruction filters           | 500 MHz and 250 MHz realized as 7-pole Cauer Chebychev filters plus thru-line output                                 |                                       |                                                |

| Pulse response                   | Rise time (10 to 90%): < 1 ns<br>Fall time (10 to 90%): < 1 ns<br>Amplitude: 0.5 Vp-p                                |                                       |                                                |

|                                  |                                                                                                                      |                                       |                                                |

<sup>1</sup> A sync clock cycle is clock/8

### **General Characteristics**

#### **LXI Class A Certified**

#### **Power**

| Line power | 100/120/220/240 VAC, 50/60 Hz, 100 watts maximum |  |

|------------|--------------------------------------------------|--|

|------------|--------------------------------------------------|--|

#### **Environmental**

Samples of this product have been type tested in accordance with the Agilent Environmental Test Manual and verified to be robust against the environmental stresses of storage, transportation, and end-use; those stresses include, but are not limited to temperature, humidity, shock vibration, altitude, and power line conditions. Test methods are aligned with IEC 60068-2 and levels are similar to MIL-PRF-28800F Class 3.

| Operating temperature | 0 to +50 degrees C (0 to 47 degrees C at 15,000 ft altitude) |

|-----------------------|--------------------------------------------------------------|

| Storage temperature   | -40 to +70 degrees C                                         |

#### **Relative humidity**

| Type tested: | 0 to 95% at 40 degrees C (non-condensing) |

|--------------|-------------------------------------------|

| Altitude     | 0 to 4500 m (15,000 ft) above sea level   |

#### Weight

5.66 kg (12.5 lb)

#### **Security**

All user data stored in volatile memory

#### **Dimensions**

| Height: | 89 mm (3.5 inch)     |

|---------|----------------------|

| Width:  | 213 mm (8.375 inch)  |

| Depth:  | 422 mm (16.625 inch) |

#### **Calibration cycle**

1 year warranty, platform calibration not required.

#### ISO compliance

This instrument is manufactured in an ISO-9001 registered facility in concurrence with Agilent Technologies, Inc. commitment to quality.

• Electrostatic Discharge Immunity – IEC 61000-4-2: passes criterion C

Testing according to IEC 61000-4-2: showed that the exposure of the data port to electrostatic discharge may interrupt operation of the N8241A/42A. Operation can be restored by reloading the desired waveforms and restarting. This required operator intervention results in a criterion C classification.

## **Ordering Information**

Figure 11. Agilent N8241A 15-bit arbitrary waveform generator LXI module

### N8241A 15-bit arbitrary waveform generator with 8 MS memory per channel

### **Options**

| N8241A-125 | 1.25 GS/s sample rate                           |

|------------|-------------------------------------------------|

| N8241A-062 | 625 MS/s sample rate                            |

| N8241A-016 | Waveform memory expansion to 16 MS per channel  |

| N8241A-300 | Enabling software for 16-bit dynamic sequencing |

| N8241A-330 | Direct digital synthesis software               |